Dr. Heinrich Riebler

Mitglied - Postdoc

- E-Mail:

- heinrich.riebler@uni-paderborn.de

- Telefon:

- +49 5251 60-5382

- Web:

- Homepage

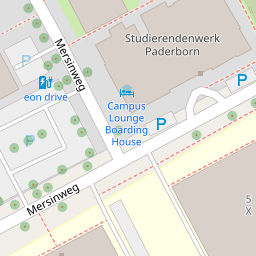

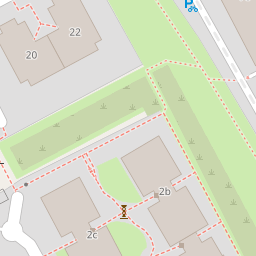

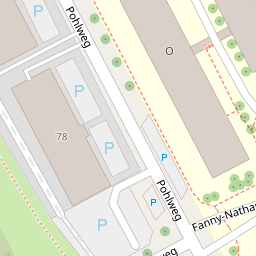

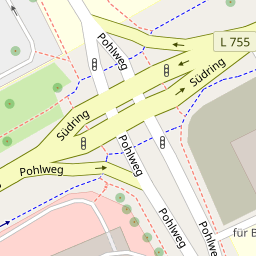

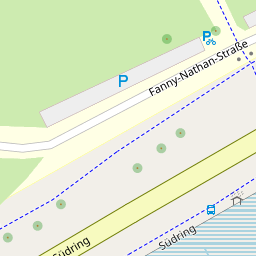

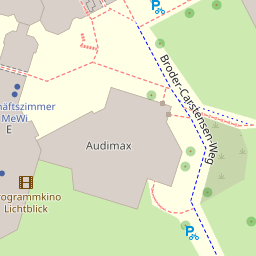

- Büroanschrift:

-

Mersinweg 5

33100 Paderborn - Raum:

- X1.119

Publikationen

Aktuelle Publikationen

FINN-HPC: Closing the Gap for Energy-Efficient Neural Network Inference on FPGAs in HPC

L. Jungemann, B. Wintermann, H. Riebler, C. Plessl, in: Proceedings of the 15th International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies, ACM, New York City, n.d.

AuroraFlow, an Easy-to-Use, Low-Latency FPGA Communication Solution Demonstrated on Multi-FPGA Neural Network Inference

G. Pape, B. Wintermann, L. Jungemann, M. Lass, M. Meyer, H. Riebler, C. Plessl, in: Proceedings of the 15th International Symposium on Highly Efficient Accelerators and Reconfigurable Technologies, n.d.

Noctua 2 Supercomputer

C. Bauer, T. Kenter, M. Lass, L. Mazur, M. Meyer, H. Nitsche, H. Riebler, R. Schade, M. Schwarz, N. Winnwa, A. Wiens, X. Wu, C. Plessl, J. Simon, Journal of Large-Scale Research Facilities 9 (2024).

A Computation of the Ninth Dedekind Number Using FPGA Supercomputing

L. Van Hirtum, P. De Causmaecker, J. Goemaere, T. Kenter, H. Riebler, M. Lass, C. Plessl, ACM Transactions on Reconfigurable Technology and Systems 17 (2024) 1–28.

A computation of D(9) using FPGA Supercomputing

L. Van Hirtum, P. De Causmaecker, J. Goemaere, T. Kenter, H. Riebler, M. Lass, C. Plessl, ArXiv:2304.03039 (2023).

Alle Publikationen anzeigen