- E-Mail:

- witschen@mail.uni-paderborn.de

- Telefon:

- +49 5251 60-1729

- Web:

- Homepage

- Büroanschrift:

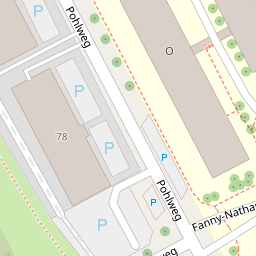

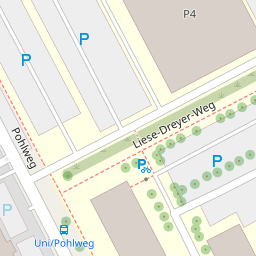

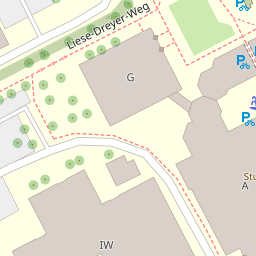

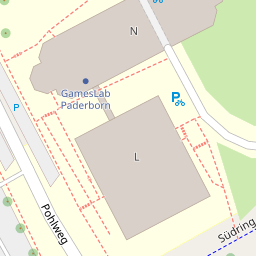

-

Pohlweg 51

33098 Paderborn - Raum:

- O3.119

Publikationen

Aktuelle Publikationen

Search Space Characterization for Approximate Logic Synthesis

L.M. Witschen, T. Wiersema, L.D. Reuter, M. Platzner, in: 2022 59th ACM/IEEE Design Automation Conference (DAC), n.d.

MUSCAT: MUS-based Circuit Approximation Technique

L.M. Witschen, T. Wiersema, M. Artmann, M. Platzner, in: Design, Automation and Test in Europe (DATE), n.d.

Frameworks and Methodologies for Search-based Approximate Logic Synthesis

L.M. Witschen, Frameworks and Methodologies for Search-Based Approximate Logic Synthesis, 2022.

Timing Optimization for Virtual FPGA Configurations

L.M. Witschen, T. Wiersema, M. Raeisi Nafchi, A. Bockhorn, M. Platzner, in: F. Hannig, S. Derrien, P. Diniz, D. Chillet (Eds.), Proceedings of International Symposium on Applied Reconfigurable Computing (ARC’21), Springer Lecture Notes in Computer Science, n.d.

Proof-carrying Approximate Circuits

L.M. Witschen, T. Wiersema, M. Platzner, IEEE Transactions On Very Large Scale Integration Systems 28 (2020) 2084–2088.

Alle Publikationen anzeigen