Dr. Tobias Wiersema

Ehemaliger

- E-Mail:

- tobias.wiersema@uni-paderborn.de

- Telefon:

- +49 5251 60-4343

- Web:

- Homepage

- Büroanschrift:

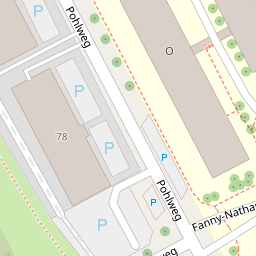

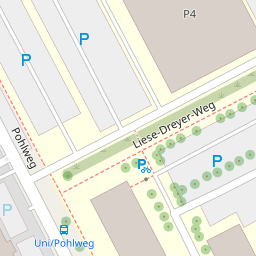

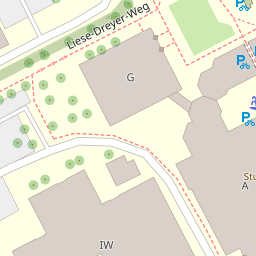

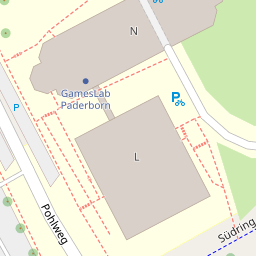

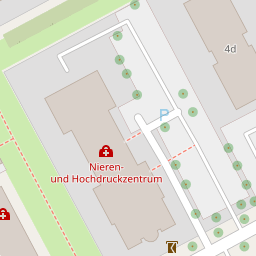

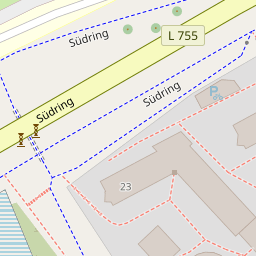

-

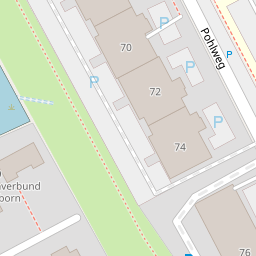

Pohlweg 51

33098 Paderborn - Raum:

- O3.125

- Sprechstunden:

by appointment

Publikationen

Aktuelle Publikationen

Post-configuration Activation of Hardware Trojans in FPGAs

Q.A. Ahmed, T. Wiersema, M. Platzner, Journal of Hardware and Systems Security (2024).

Search Space Characterization for Approximate Logic Synthesis

L.M. Witschen, T. Wiersema, L.D. Reuter, M. Platzner, in: 2022 59th ACM/IEEE Design Automation Conference (DAC), n.d.

MUSCAT: MUS-based Circuit Approximation Technique

L.M. Witschen, T. Wiersema, M. Artmann, M. Platzner, in: Design, Automation and Test in Europe (DATE), n.d.

Guaranteeing Properties of Reconfigurable Hardware Circuits with Proof-Carrying Hardware

T. Wiersema, Guaranteeing Properties of Reconfigurable Hardware Circuits with Proof-Carrying Hardware, Paderborn University, Paderborn, 2021.

Timing Optimization for Virtual FPGA Configurations

L.M. Witschen, T. Wiersema, M. Raeisi Nafchi, A. Bockhorn, M. Platzner, in: F. Hannig, S. Derrien, P. Diniz, D. Chillet (Eds.), Proceedings of International Symposium on Applied Reconfigurable Computing (ARC’21), Springer Lecture Notes in Computer Science, n.d.

Alle Publikationen anzeigen