- E-Mail:

- sybille.hellebrand@uni-paderborn.de

- Telefon:

- +49 5251 60-3002

- Web:

- Homepage

- Büroanschrift:

-

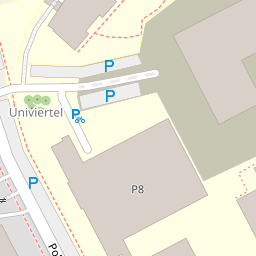

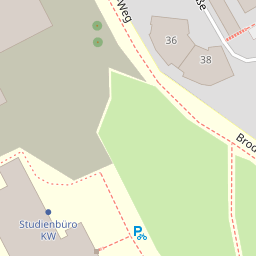

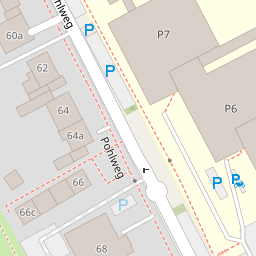

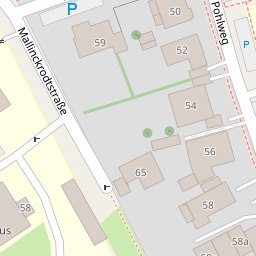

Pohlweg 47-49

33098 Paderborn - Raum:

- P1.6.08.1

- Sprechstunden:

nach Vereinbarung

Publikationen

Aktuelle Publikationen

Time and Space Optimized Storage-based BIST under Multiple Voltages and Variations

H. Jafarzadeh, F. Klemme, H. Amrouch, S. Hellebrand, H.-J. Wunderlich, in: European Test Symposium, The Hague, Netherlands, May 20-24, 2024, IEEE, n.d., p. 6.

Vmin Testing under Variations: Defect vs. Fault Coverage

H. Jafarzadeh, F. Klemme, H. Amrouch, S. Hellebrand, H.-J. Wunderlich, in: IEEE Latin American Test Symposium (LATS), Maceió, Brazil, April 9-12, 2024, IEEE, n.d., p. 6.

Functional Safety and Reliability of Interconnects throughout the Silicon Life Cycle

S. Hellebrand, S. Sadeghi-Kohan, H.-J. Wunderlich, in: International Symposium of EDA (ISEDA), Xi’an, China, May 10-13, 2024, n.d., p. 1.

Robust Test of Small Delay Faults under PVT-Variations

H.-J. Wunderlich, H. Jafarzadeh, S. Hellebrand, in: International Symposium of EDA (ISEDA), Xi’an, China, May 10-13, 2024, n.d., p. 1.

Modeling Crosstalk-induced Interconnect Delay with Polynomial Regression

A. Stiballe, J.D. Reimer, S. Sadeghi-Kohan, S. Hellebrand, Modeling Crosstalk-Induced Interconnect Delay with Polynomial Regression, 37. ITG / GMM / GI -Workshop “Testmethoden und Zuverlässigkeit von Schaltungen und Systemen” (TuZ’24), Feb. 2024, Darmstadt, Germany, 2024.

Alle Publikationen anzeigen

Lehre

Laufende Lehrveranstaltungen

- Topics in Systems Engineering - Test and Fault Tolerance

- Qualitätssicherung mikroelektronischer Systeme

- Projektseminar Datentechnik

- Forschungsseminar Datentechnik

- Digitaltechnik

- Algorithms and Tools for Test and Diagnosis of Systems on Chip

- Algorithms and Tools for Test and Diagnosis of Systems on Chip