Abdul Rehman Tareen

Paderborn Center for Parallel Computing (PC2)

Mitglied - Wissenschaftlicher Mitarbeiter

Research Associate

- E-Mail:

- abdul.rehman.tareen@uni-paderborn.de

- Telefon:

- +49 5251 60-1730

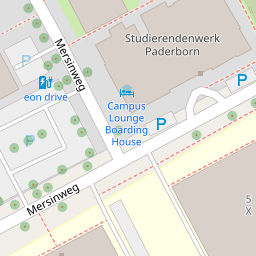

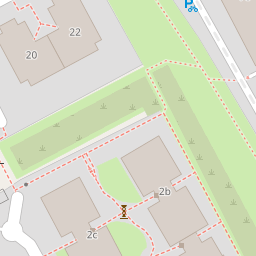

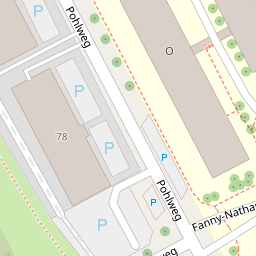

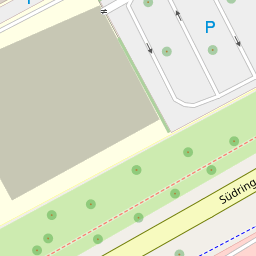

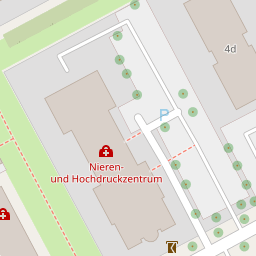

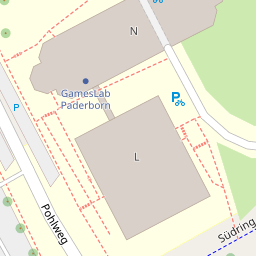

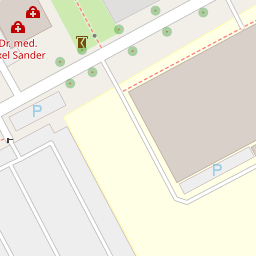

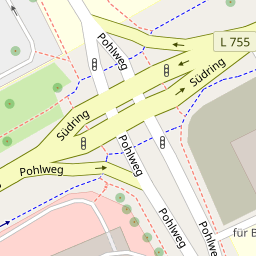

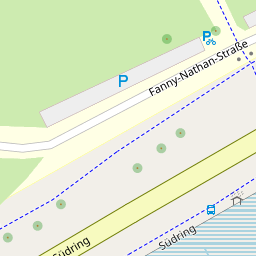

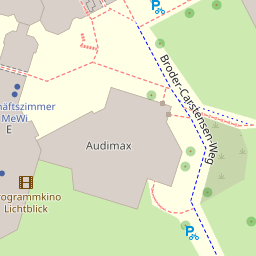

- Büroanschrift:

-

Mersinweg 5

33100 Paderborn - Raum:

- X0.116

Publikationen

Aktuelle Publikationen

HiHiSpMV: Sparse Matrix Vector Multiplication with Hierarchical Row Reductions on FPGAs with High Bandwidth Memory

A.R. Tareen, M. Meyer, C. Plessl, T. Kenter, in: 2024 IEEE 32nd Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), IEEE, 2024.

Alle Publikationen anzeigen