- E-Mail:

- peer.adelt@uni-paderborn.de

- Phone:

- +49 5251 60-6304

- Office Address:

-

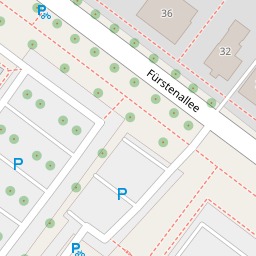

Fürstenallee 11

33102 Paderborn - Room:

- F0.407

Publications

Latest Publications

The Scale4Edge RISC-V Ecosystem

W. Ecker, P. Adelt, W. Müller, R. Heckmann, M. Krstic, V. Herdt, R. Drechsler, G. Angst, R. Wimmer, A. Mauderer, R. Stahl, K. Emrich, D. Mueller-Gritschneder, B. Becker, P. Scholl, E. Jentzsch, J. Schlamelcher, K. Grüttner, P.P. Bernardo, O. Brinkmann, M. Damian, J. Oppermann, A. Koch, J. Bormann, J. Partzsch, C. Mayr, W. Kunz, in: In Proceedings of the Design Automation and Test Conference and Exhibition (DATE 2022), 2022.

Register and Instruction Coverage Analysis for Different RISC-V ISA Modules

P. Adelt, B. Koppelmann, W. Müller, C. Scheytt, in: MBMV 2021 - Methods and Description Languages for Modelling and Verification of Circuits and Systems; GMM/ITG/GI-Workshop, VDE, Munich, DE, 2021.

QEMU zur Simulation von Worst-Case-Ausführungszeiten

P. Adelt, B. Koppelmann, W. Müller, C. Scheytt, in: MBMV 2021 - Methods and Description Languages for Modelling and Verification of Circuits and Systems; GMM/ITG/GI-Workshop, VDE, Munich, DE, 2021.

Register and Instruction Coverage Analysis for Different RISC-V ISA Modules

P. Adelt, B. Koppelmann, W. Müller, C. Scheytt, in: Workshop Methoden Und Beschreibungssprachen Zur Modellierung Und Verifikation von Schaltungen Und Systemen (MBMV 2021), 2021.

A Scalable Platform for QEMU Based Fault Effect Analysis for RISC-V Hardware Architectures

P. Adelt, B. Koppelmann, W. Müller, C. Scheytt, in: MBMV 2020 - Methods and Description Languages for Modelling and Verification of Circuits and Systems; GMM/ITG/GI-Workshop, Stuttgart, DE, 2020.

Show all publications