Dr. Tobias Kenter

Member - PostDoc

- E-Mail:

- kenter@uni-paderborn.de

- Phone:

- +49 5251 60-4340

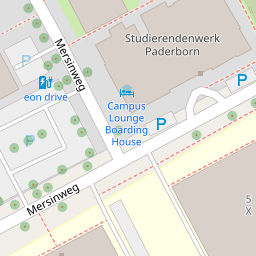

- Office Address:

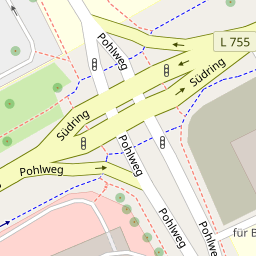

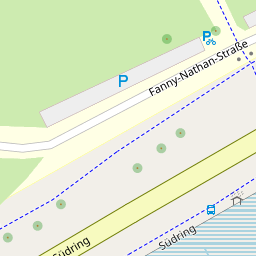

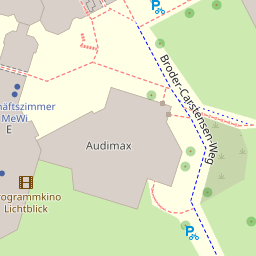

-

Mersinweg 5

33100 Paderborn - Room:

- X1.119

Publications

Latest Publications

Optimizing Communication for Latency Sensitive HPC Applications on up to 48 FPGAs Using ACCL

M. Meyer, T. Kenter, L. Petrica, K. O’Brien, M. Blott, C. Plessl, ArXiv:2403.18374 (2024).

Characterizing Microheterogeneity in Liquid Mixtures via Local Density Fluctuations

M. Lass, T. Kenter, C. Plessl, M. Brehm, Entropy 26 (2024).

Optimisation and Evaluation of Breadth First Search with oneAPI/SYCL on Intel FPGAs: from Describing Algorithms to Describing Architectures

K. Olgu, T. Kenter, J. Nunez-Yanez, S. Mcintosh-Smith, in: Proceedings of the 12th International Workshop on OpenCL and SYCL, ACM, 2024.

Noctua 2 Supercomputer

C. Bauer, T. Kenter, M. Lass, L. Mazur, M. Meyer, H. Nitsche, H. Riebler, R. Schade, M. Schwarz, N. Winnwa, A. Wiens, X. Wu, C. Plessl, J. Simon, Journal of Large-Scale Research Facilities 9 (2024).

StencilStream: A SYCL-based Stencil Simulation Framework Targeting FPGAs

J.-O. Opdenhövel, C. Alt, C. Plessl, T. Kenter, in: 2024 34th International Conference on Field-Programmable Logic and Applications (FPL), IEEE, 2024.

Show all publications