- E-Mail:

- wmueller@hni.uni-paderborn.de

- Phone:

- +49 5251 60-6352

- Web:

- Homepage

- Office Address:

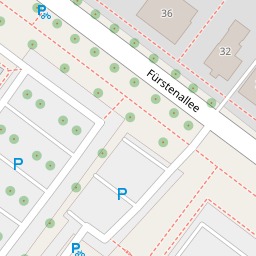

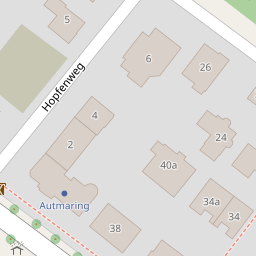

-

Fürstenallee 11

33102 Paderborn - Room:

- F0.431

Research

Publications

Latest Publications

Verilator and FireSim RTL Simulations on a HPC Cluster: A Comparative Case Study

K.A. Hannemann, H.B. Bütün, W. Müller, J.C. Scheytt, in: MBMV 2025 - 28. Workshop Methoden Und Beschreibungssprachen Zur Modellierung Und Verifikation von Schaltungen Und Systemen, VDE Verlag, Warnemünde, 2025.

Case Study on Combining Open-Source Tool Flows for Grids of Processing Cells

L. Luchterhandt, V. Govindasamy, Y. Wang, R. Dömer, W. Müller, J.C. Scheytt, in: OSSMPIC - Open Source Solutions for Massively Parallel Integrated Circuits, Lyon, France, 2025.

A Scalable RISC-V Hardware Platform for Intelligent Sensor Processing

P. Palomero Bernardo, P. Schmid, O. Bringmann, M. Iftekhar, B. Sadiye, W. Müller, A. Koch, E. Jentsch, A. Sauer, I. Feldner, W. Ecker, in: DATE 24 - Design Automation and Test in Europe, 2024.

Implementation of Different Communication Structures for a Rocket Chip Based RISC-V Grid of Processing Cells

L. Luchterhandt, T. Nellius, R. Beck, R. Dömer, P. Kneuper, W. Müller, B. Sadiye, in: MBMV 2024 - 27. Workshop Methoden Und Beschreibungssprachen Zur Modellierung Und Verifikation von Schaltungen Und Systemen“, VDE Verlag, 2024.

Scale4Edge – Scaling RISC-V for Edge Applications

W. Ecker, M. Krstic, M. Ulbricht, A. Mauderer, E. Jentzsch, A. Koch, B. Koppelmann, W. Müller, B. Sadiye, N. Bruns, R. Drechsler, D. Müller-Gritschneder, J. Schlamelcher, K. Grüttner, J. Bormann, W. Kunz, R. Heckmann, G. Angst, R. Wimmer, B. Becker, T. Faller, P. Palomero Bernardo, O. Brinkmann, J. Partzsch, C. Mayr, in: RISC-V Summit Europe 2023, Barcelona, Spain, June 2023., 2023.

Show all publications

Teaching

Current Courses

- Topics in Systems Engineering - IC Design

- Projekt Angewandte Programmierung

- Electronic System Design (Project)

- Electronic System Design (Project)

- Advanced VLSI Design

- Advanced VLSI Design